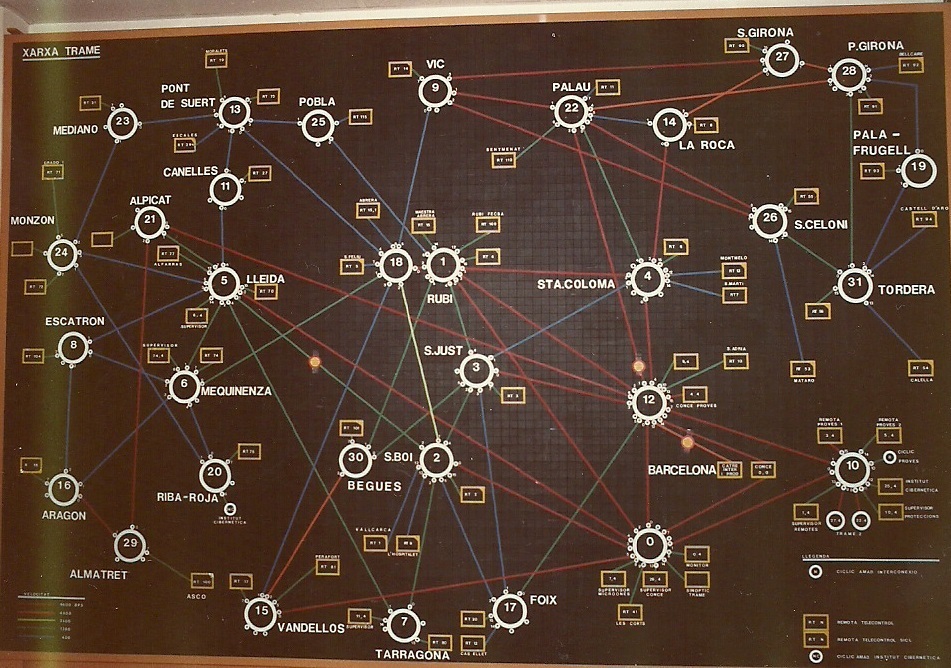

La xarxa TRAME es va desenvolupar a ENHER als anys 70.

A ENHER, per un cantó teniem el CONCE, Control Central de la xarxa elèctrica, que pujava o baixava la producció segons convingués.

Per l'altre banda, teniem el SICL, manegador de les estacions remotes, on es prenien mesures, es detectaven alarmes i s'efectuaven actuacions remotes.

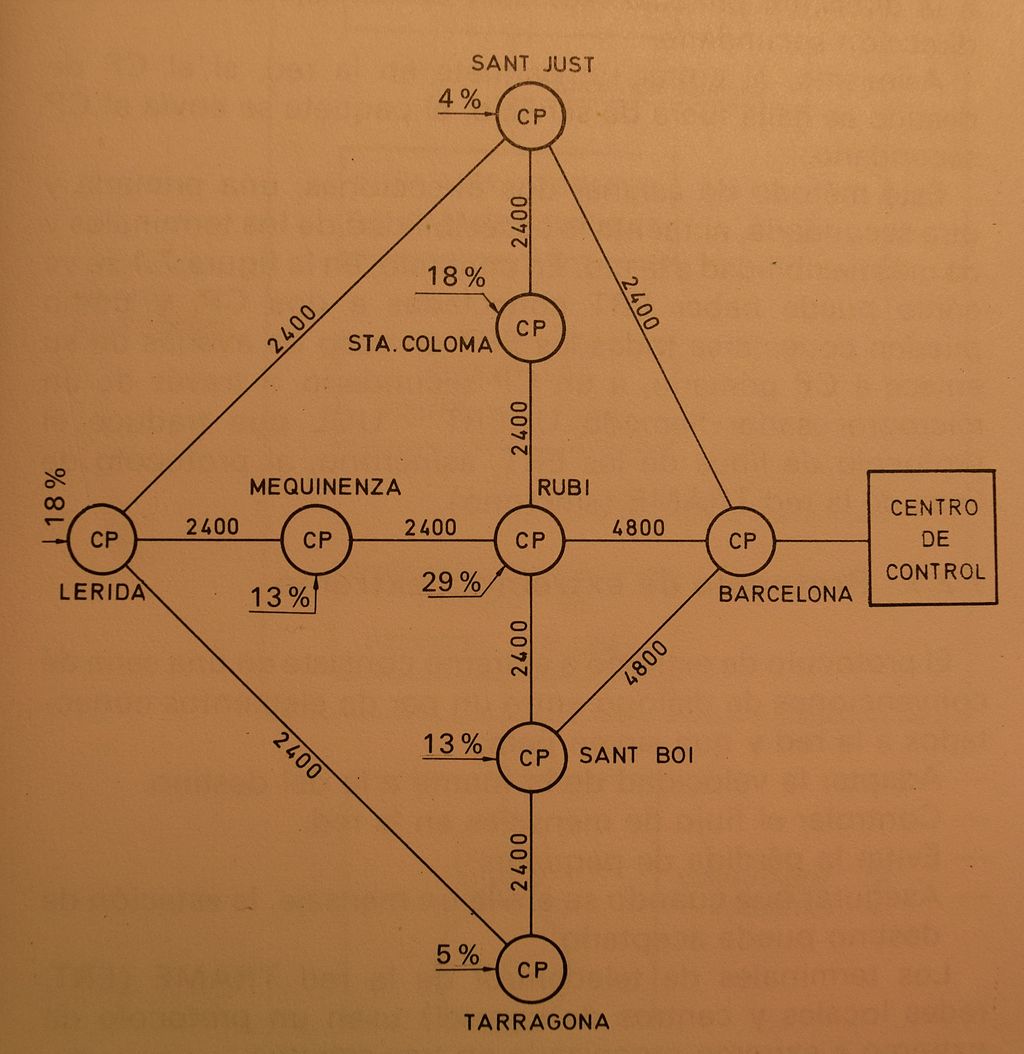

Calia conectar el CONCE amb els SICL - això és el TRAME.

El conjunt CONCE + TRAME + SICL es un SCADA

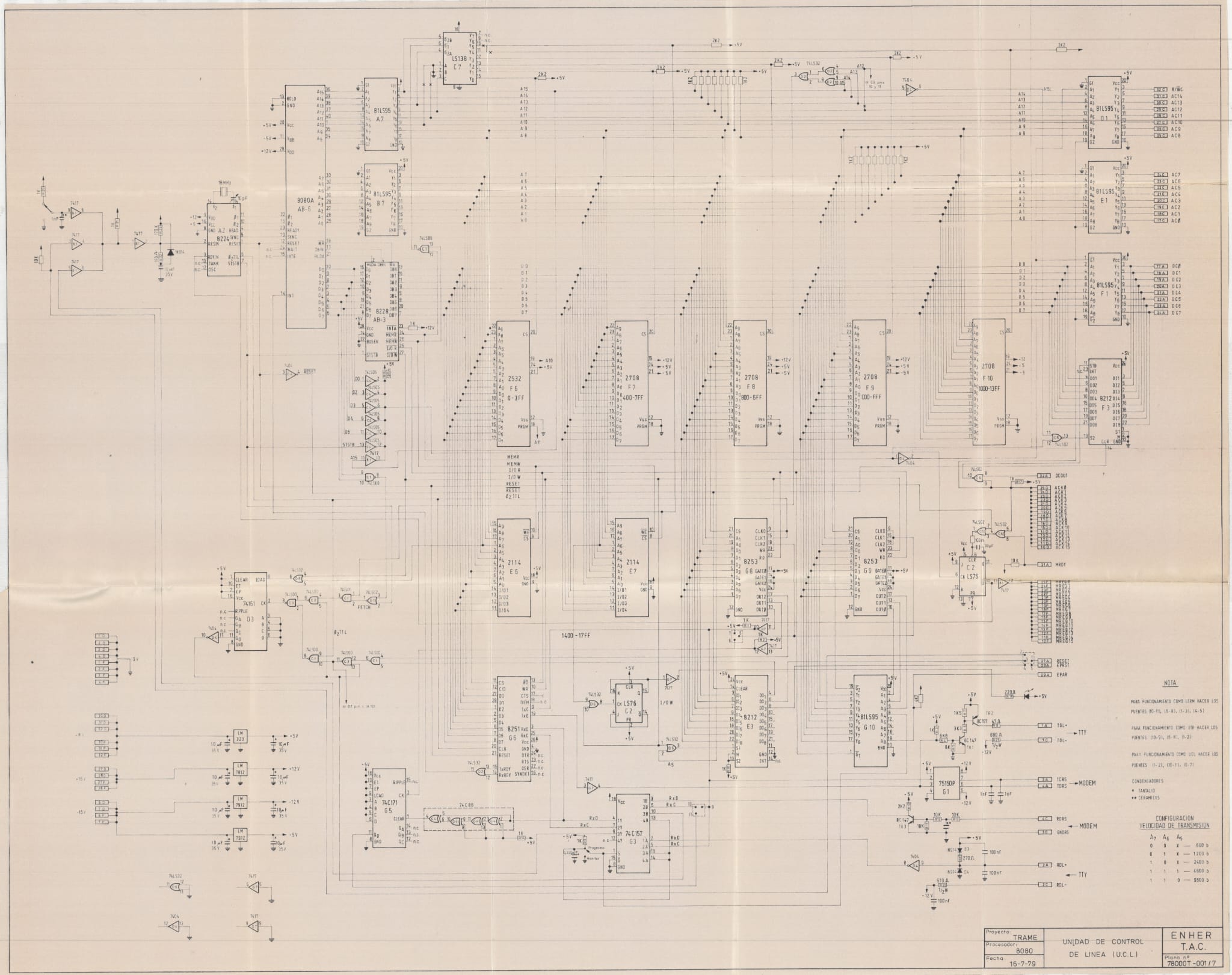

Es van fer algunes plaques amb la CPU Intel 8080.

El segon hardware es basava en una placa amb un xip Z80 de Zylog com CPU, aixi com 2 SIOs (serial input/output) de Zylog, 3 CTCs (counter/timer) també de Zylog, i una memoria de 64 KB entre ROM (programa) i RAM (dades)

See Z80 peripherals

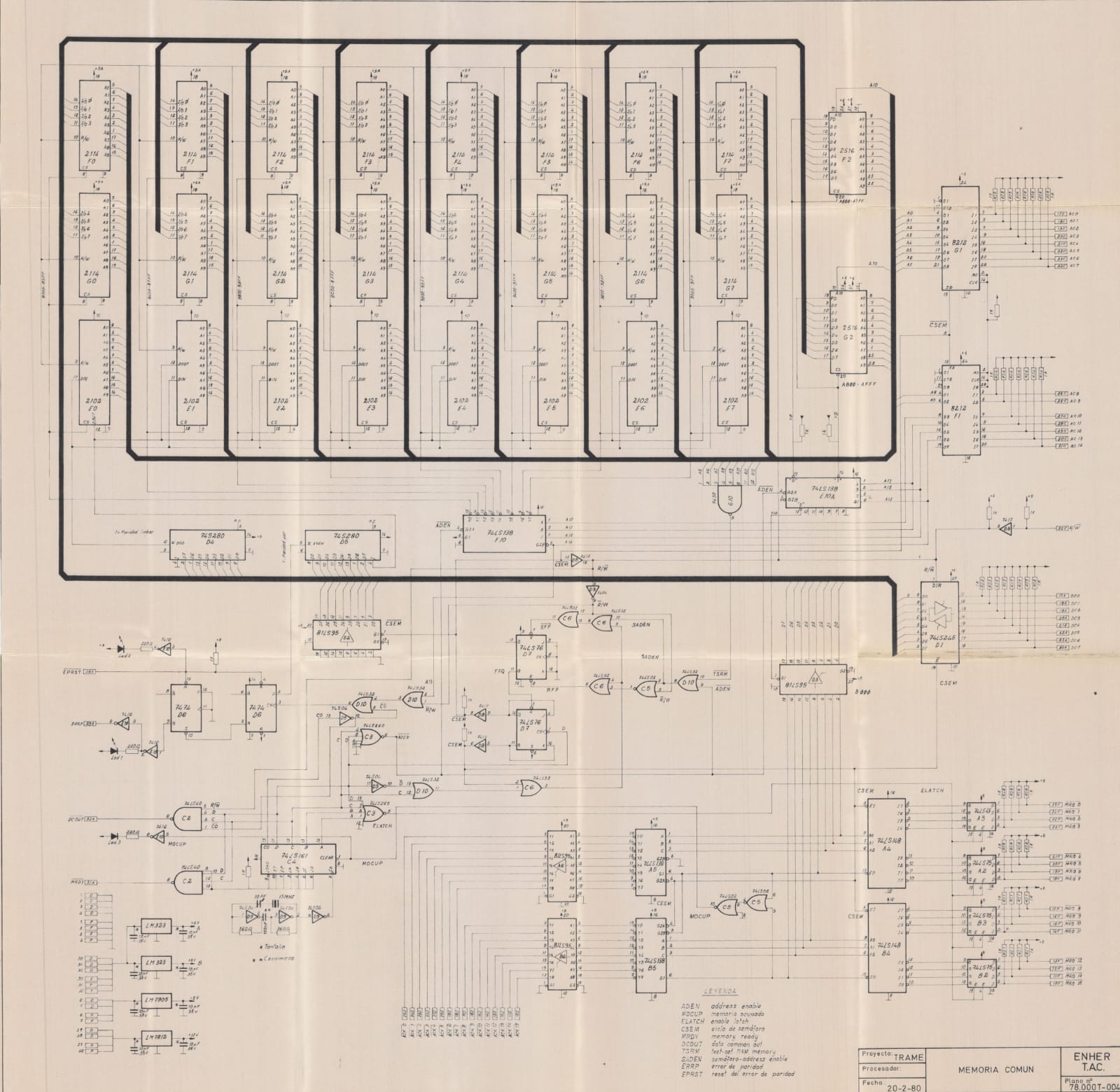

Un node TRAME consisteix en 17 plaques com a màxim : fins a 16 plaques UTR o UCL, que compartien una placa MC, Memoria Comú, que és on es fa la commutació de missatges.

Com que cada SIO pot manegar 2 linies de dades, i tenim 2 SIOs per placa, aixo vol dir que una placa pot manegar 4 linies de dades

Com que un node de TRAME pot tenir fins a 16 plaques, aixo vol dir que un node TRAME pot manegar fins a 64 linies de dades.

Una de les plaques del node TRAME era la placa "mestre" i era la encarregada de inicialitzar les dades de la Memoria Comú abans que la resta de plaques entressin en funcionament.

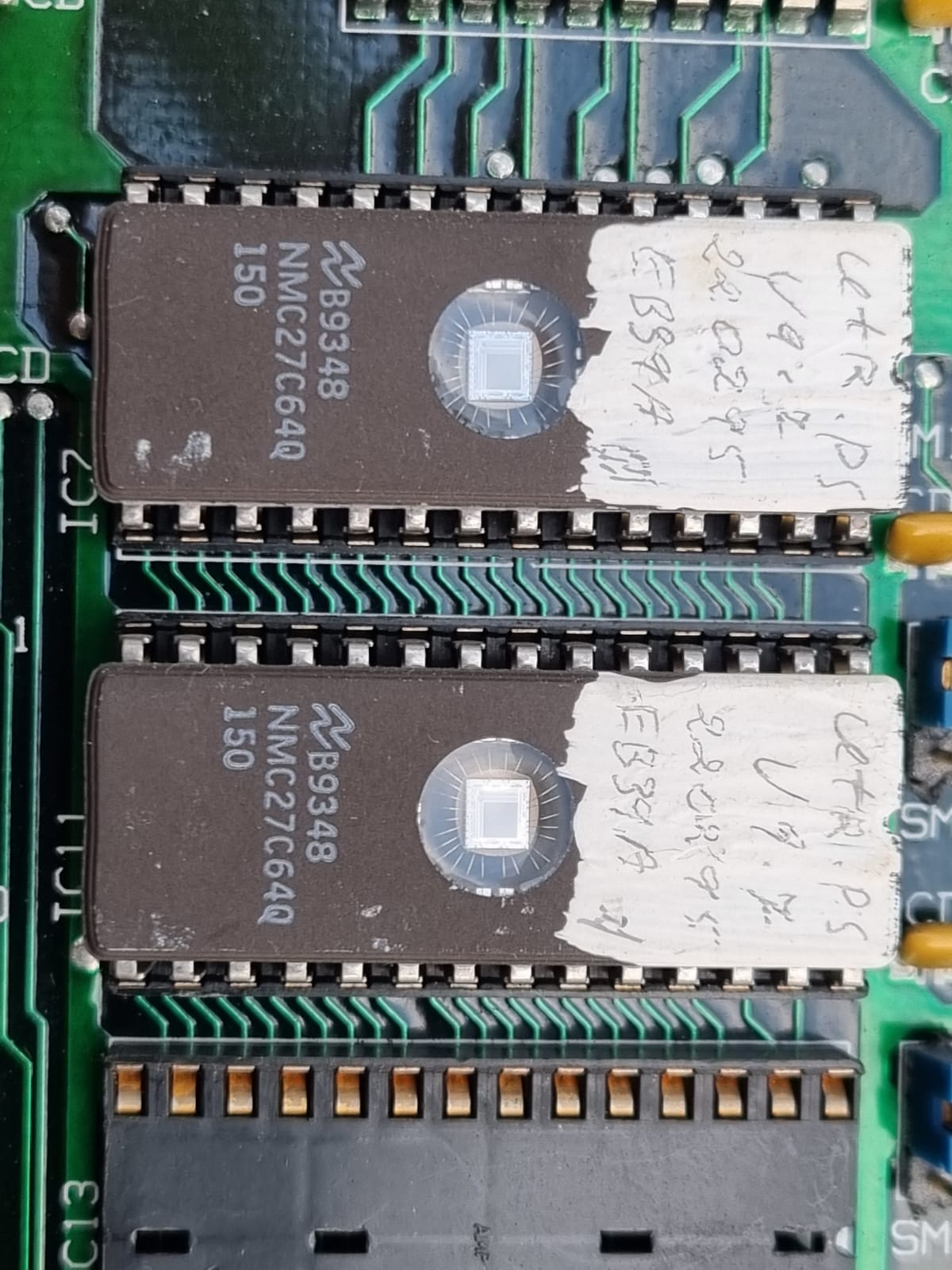

Per programar la placa feiem servir una ROM com 27C64A (28 pins), de 64 K bits, es a dir 8 K words de 8 bits

Abans per programar-les feiem servir un Data/IO, ara es T48 TL866II programmer

Ens val per llegir una 27C64 ?

- nice page :

- official website: http://www.xgecu.com/EN

- T48 (TL866-3G) programmer manufacturer : Haikou Xingong Electronics Co., Ltd.

- T48 (TL866-3G) English manual (similar as TL866II/T56)

Compra T48 TL866 :

- Amazon - 73 € {***} - Fabricante : XGecu ; ASIN : B0BLSW7B22

- eBay - 56 $

- Wallapop - 145 €

- AliExpress - 45,71 € + 6,48 € enviament

Altres links :

- T48 supported device IC list : AM27C64 - @DIP28 ; AM27C64 - @PLCC32

See DIP28 versus PLCC32 (dual-in-line versus Plastic Leaded Chip Carrier, 32 pins, quadrat) - Data/IO @ eBay

From "T56_TL866II USER GUIDE.pdf" :

- go to xgecu homepage, then download section

- download the XgproVxxxx_setup.exe file

Altres links :

- {***} latest software download link (will be updated in the future)

If you cannot download or downloading speed is very slow, please send message to us, we will send to your mail box - email: xgecupro@gmail.com - latest software xgproV1255_setup.rar (31087464) or V1266A and 1267

- download newest XGecu T56/T48/TL866II software : forums.xgecu

- Z80 heaven - A place for all the z80 info you'll want

- opcode reference chart

- instruction set

- Z80 opcodes, as "0xF3" -> "DI"

- Z80 Undocumented Instructions

En treballar per interrupcions, es bàsic saber-ne la programacio, principalment per saber on tenen l'adressa del codi que executarà en rebre una interrupcio.

Podem començar per esbrinar les seves adreces, on s'hi fan les instruccions "IN" o "OUT" ( o putsé només un POST() ... )

CTC PDF, SCC = advanced SIO, Z80 CPU

En el software del Z80 hi ha diferents vessants

- (a) el sistema operatiu, suport de la resta de funcionalitats

- (b) el protocol UTR i UCL, metode per transferir informacio entre 2 punts de la xarxa connectats per una linia de dades

- (c) el control de encaminament, per decidir el proper enllaç que ha de seguir un missatge

- (d) la arquitectura del node, que permet el salt de una linia a una altre per via de la Memoria Comú (MC en endevant)

- (e) el control de xarxa, es a dir la monitoritzacio

Evidentment, la clau del funcionament de la xarxa TRAME esta en el algorisme de encaminament, que determina cap on s'ha de enviar un missatge que ve de un determinat origen i porta indicada una certa destinació.

Tenim dos tipus de software de contol de linia :

- UTR - Unio Terminal Remota - protocol propi, asincrone - comunicacio del TRAME amb el exterior, sigui SICL o CONCE

- UCL - Unitat de Control de Linia - comunicacio entre nodes, protol propi, síncrone

La placa es programava en ensamblador, en uns equips HP-64000

Una mostra del soft del 8080

Un node TRAME es un "embedded system", sistema autónom sense intervenció humana exterior,

preparat per fer una tasca determinada, en aquest cas, la commutacio de missatges.

Es reb un missatge de una linia, es mira la seva destinacio, es busca el millor cami (millor linia de sortida) i s'hi envia el missatge via la MC.

Si es reb un missatge des la MC, o es per nosaltres (monitoritzacio de la xarxa) o es per la linia associada a l'adreça de memoria de on ha arribat

Qualsevol tasca de un node TRAME està sempre activada per un event, una interrupcio, com rebre un missatge de l'exterior (interrupció de la SIO) o un timeout (interrupció del CTC)

Per aquest motiu vam implementar un petit sistema operatiu, on les tasques esperen en un semàfor a que es produeixi un succés extern i llavors fan el que calgui.

El codi dins la regio critica (interrupció) sempre serà curt i lo unic que fa es

- posar el missatge en una cua

- activar el semafor associat a la cua - operacio "signal()"

Les parts del nostre sistema operatiu son :

- una llista de processos que poden adquirir la CPU

- uns semafors (regions critiques) que permeten despertar un procés en el moment de produir-se un event, operacio "signal()", o bloquejar-lo fins que succeeixi - operacio "wait()"

- unes cues de missatges (regions critiques) que enmagatzemen els missatges esperant a ser processants

- una serie de temporitzadors que ens protegeixen de la finalitzacio errónia de una operació

Una regió crítica és una variable (o un conjunt de variables) que és accedida des 2 processos, algun dels quals pot fer-ho des una interrupció. Per tenir consistència en els seus valors, es protegeixen inhibint les interrupcions mentre la tasca fora de interrupcio les modifica.

Els processos implementats en la xarxa TRAME es defineixen per 2 adreces :

- una en ROM, on comença el seu codi

- una en RAM, on es trobaran les seves variable i s'ubica el seu stack

La estructura típica de un procés és :

Els processos que implementen el control de linia de un node TRAME son de tipus "non-preemptive", es a dir que un cop agafen el control, l'han de abandonar voluntariament, es a dir, no hi ha "preempt" (perdua de la CPU) per time-slice (acabament de un periode). Es va escollir aquest mètode pensant que totes les tasques son igual de importants, i que seran rapides i curtes. També, ens estalviem el canvi de contexte, cosa que fa mes rapid el sistema.

Non-preemptive scheduling is a method that allows the operating system to run a process until it finishes its execution, blocks, or voluntarily relinquishes the CPU. This means that a process cannot be preempted or interrupted by another process once it starts running. Non-preemptive scheduling can simplify the design and implementation of the operating system, as there is no need to deal with the issues of preemption, such as context switching, synchronization, and deadlock prevention.

Preemptive scheduling is a method that allows the operating system to interrupt a running process and switch to another process that has a higher priority or needs urgent attention. This means that a process can be preempted or stopped at any time before it completes its execution.

Per protegir el sistema del malfuncionament de un dels processos que podria agafar la CPU i no retornar-la mai a les altres tasques, se implementa un "watch-dog" per hardware. És un monostable "one-shot" que es va reiniciant constantment des el bucle de canvi de procés. De no produir-se aquest reinici en un determinat període, el hardware reiniciarà la placa.

La llista generica dels processos que tenim en una placa TRAME pot ser :

- recepció de un missatge de linia

- transmissio de missatges cap a la linia

- tractament de un timeout

- tractament de un missatge de la MC (Memoria Comu)

Cadascun d'ells ve iniciat per una interrupcio, que posara el event en una cua i es despertarà un proces per tramitar-lo.

Quan rebem un missatge de un altre node mitjançant la SIO, despres de verificar-lo hem de enviar un ACK (si l'acceptem) o un NACK (si el rebutgem).

Si l'hem acceptat i és de dades, hem de determinar el seu seguent salt, que sempre serà per la via de la Memoria Comú (MC).

En canvi si es de control de linia (un ACK o un NACK), hem de re-enviar el missatge (si rebem un NACK) o descartar-lo (si es un ACK).

Si hem enviat un missatge de control de linia (ACK o NACK), no hem de fer res mes.

Si hem enviat un missatge de dades, hem de engegar un temporitzador per limitar el temps de espera de la resposta.

Finalment, mirarem a la cua de missatges per enviar si hi ha mes feina per la tasca que envia missatges per la línia. Si n'hi ha, s'enviarà per la línia si la finestra és oberta, o es queda retingut a la cua en cas de estar la finestra tancada.

A tots els efectes es considera equivalent a rebre un NACK.

Es a dir, provocarà el re-enviament de un missatge si no s'ha arribat al comptatge màxim.

Quan trobem un missatge a la MC (on li ha posat una altra placa del nostre node), lo unic que hem de fer es posar-lo a la cua de transmissi associada a la seva destinació, que serà buidada per la tasca de enviament cap a la linia.

Començarem per la UTR, que sembla mes senzilla

Unitat de Control de Línia - es feia servir per comunicar 2 nodes de TRAME

Llegim la EEPROM per obtenir el software de la UTR/UCL

Tenim les EEPROMs de 5 plaques a "/home/sebas/dades/enher/5_EEPROMs"

3 UCLs v 9.7 i 2 UTRs v 9.7 - una PS i una PSM

A internet trobo :

- github S Arnau

Comentaris en alemà ; llegeix el fitxer "EPROM" - Mark Incley - dz80@inkland.org

dZ80 2.0 requires the LUA 4.0 - download here

It should be unzipped so that the lua folder appears within the dZ80 folder as "Lua". - z80dasm.c at seanriddle.com

/* Z80dasm.c - a Z80 opcode disassembler */ /* Version 1.1 19-MAY-96 */ /* Copyright © 1996 Sean Riddle */ /* Homepage : http://www.seanriddle.com */

email: me at seanriddle dot com = me@seanriddle.com

- maziac z80 dismblr

- foro Z80 heaven

- Lovable, from JMS {20250510}

Amb el "Software Manager" del Minie trobo "z80dasm v 1.1.6-1"

- Homepage {gone}

- At Ubuntu

- z80dasm Linux man page : "z80dasm -h"

- report bugs to tomaz.solc@tablix.org

- Linux Mint z80 dasm community {empty}

Se instala a

Primer juntem les 2 EPROMs :

... i el fem servir a

M'agradaria executar el ".BIN" que tinc en un emulador, veure la memoria, els registres, les adreces de I/O, etc

També puc entrar un ".HEX"

rz80 homepage, George Phillips <george@48k.ca>

Amb la nostra EEPROM :

No agafa el contingut de la 2a EEPROM ...

Una vez que tienes el archivo binario que contiene el código de la EPROM, el siguiente paso es desensamblarlo.

El archivo binario puede contener código máquina o datos en un formato específico,

por lo que necesitarás una herramienta que convierta ese código en un formato legible.

- IDA Pro (Interactive DisAssembler): Una herramienta avanzada que puede desensamblar código binario para una variedad de arquitecturas.

- Ghidra: Herramienta de ingeniería inversa de código abierto desarrollada por la NSA que también permite desensamblar y analizar binarios.

software reverse engineering suite of tools url - Radare2: Un conjunto de herramientas para ingeniería inversa que incluye un desensamblador.

free reversing toolkit - Objdump: Herramienta que puede desensamblar archivos binarios en sistemas Unix-like (como Linux).

wiki